The ISC High Performance Conference is the place-to-be to discuss important topics and trends in the fields of HPC, Machine Learning and High Performance Data Analysis. The international conference for High Performance Computing (HPC) will take place in Hamburg from May 21 – 25 May.

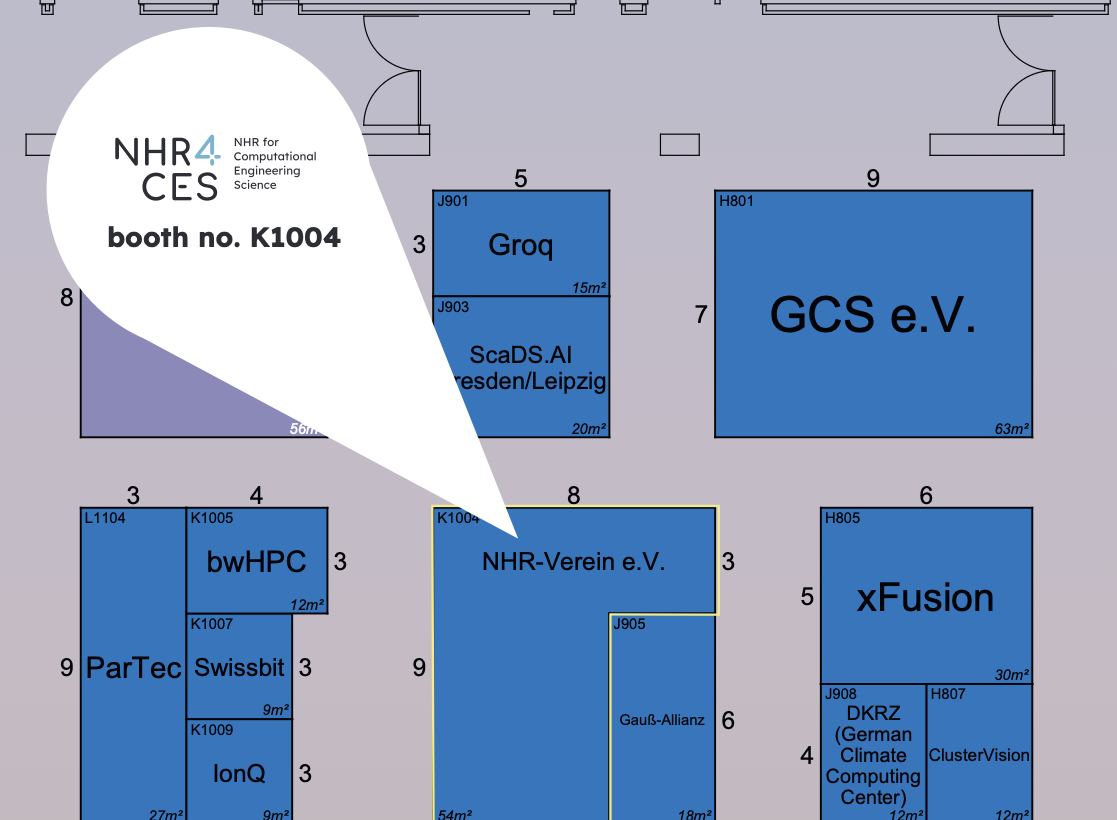

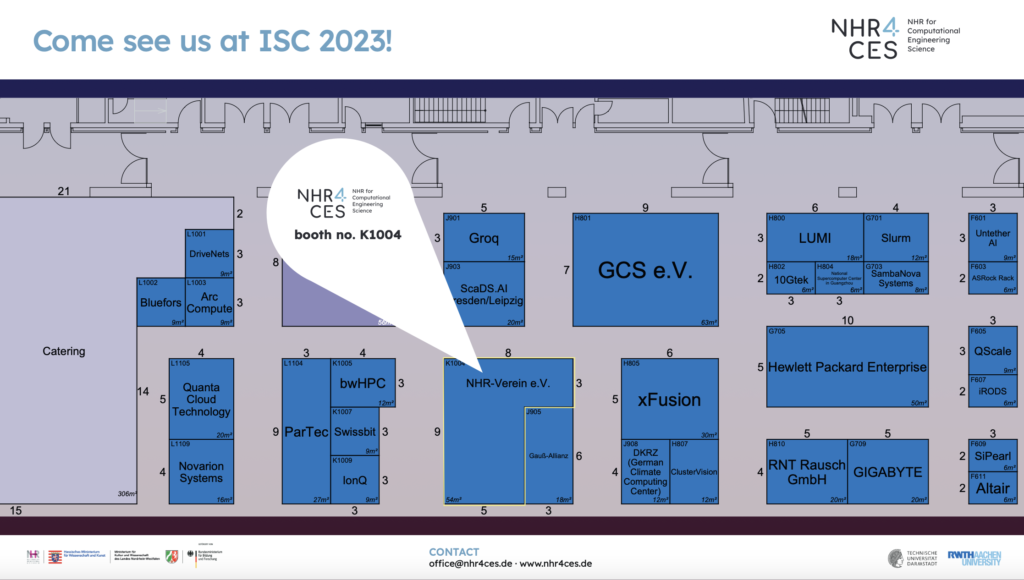

Together with the other NHR centers, NHR4CES will be present at the NHR Alliance booth (booth number K1004). From Monday to Wednesday, our HPC experts will be available for interested people to discuss infrastructure, access to computational time or our trainings and workshops. We will also host the so-called Sofa Talks again. We established this format at ISC last year and are continuing it this year, to offer an insight into our work and use the ISC as a place for exchange and communication. We invite guests to discuss relevant topics with them in a relaxed, personal atmosphere in our Sofa Corner.

Dr. Tim Gerrits from our CSG Visualization will present the first Sofa Talk: Current Challenges in Visualization for HPC Current Challenges in Visualization for HPC – How AI, Accessibility and Innovation Change Visualization Requirements. On Monday, May 22 at 4.30 pm. He and his guest will talk about Visualization as a critical aspect of High-Performance Computing that helps researchers and scientists gain insights into complex data. With advancements in technologies such as better hardware and advanced AI models, the possibilities for visualization techniques have expanded significantly, leading to a greater emphasis on accessibility. In this talk, we want to discuss how these challenges are impacting visualization experts already today and which strategies exist to tackle them. His guests are James Kress, Visualization Scientist at the KAUST Visualization Core Laboratory, François Mazen, Assistant Director of Scientific Visualization at Kitware Europe, Jens Henrik Göbbert, Scientific Assistent at Jülich Supercomputing Centre, Michael Böttinger, Group Head Visualization and Public Relations at Deutsches Klimarechenzentrum, David Pugmire, Distinguished Scientist, Visualization Group Lead at Oak Ridge National Laboratory.

On Tuesday, May 23, Dr. Christian Terboven, member of the CSG Parallelism and Performance, hosts the Sofa Talk: NHR: Benchmarks + TCO. While HPL and Stream benchmarks have a long tradition in HPC cluster procurements and acceptance tests, they do not reflect the real-world usage of an HPC cluster that often runs multi-node and/or memory-bound jobs. To evaluate the real value of an HPC system, relevant and real-world applications should be included in the request for proposals. The goal of this meeting is to continue the discussion of current HPC procurement processes in NHR and to support the corresponding future project in establishing methodologies and best practices for NHR-specific benchmarking and TCO modeling.

On Wednesday, May 24, Marc-André Hermanns will invite his guests to discuss Programming Model Dev. at 1.45 pm, while Dr. Benjamin Juhl – both from our infrastructure team – hosts his Sofa Talk regarding Software licences in NHR at 12.30 pm. NHR centers aim to attract users from all of Germany, and provide them with the expertise outlined in the center’s research expertise profile – e.g. atomistic simulations or deep learning. This expertise of course extends to the software stack provided at the NHR clusters. However traditional license agreements for university software have in the past often limited the allowed users to members of that organization. The goal of this sofa talk is to exchange experience with adjusting current license agreements, and discuss requirements for negotiating future license agreements. His guests are Thomas Zeiser, Friedrich-Alexander-Universität Erlangen-Nürnberg, Robert Schade, PC2, and Marc-André Hermanns, RWTH Aachen University

We will also be present at the conference with a tutorial and other activities.

Dr. Christian Terboven presents the tutorial Advanced OpenMP: Performance and 5.2 Features on Sunday, May 21, 9.00 am – 1.00 pm in Hall Y6, 2nd floor. With the increasing prevalence of multicore processors, shared-memory programming models are essential. OpenMP is a popular, portable, widely supported and easy-to-use shared-memory model. Developers usually find OpenMP easy to learn. However, they are often disappointed with the performance and scalability of the resulting code. This disappointment stems not from shortcomings of OpenMP, but rather from the lack of depth with which it is employed. Our “Advanced OpenMP Programming” tutorial addresses this critical need by exploring the implications of possible OpenMP parallelization strategies, both in terms of correctness and performance. While we quickly review the basics of OpenMP programming, we assume attendees understand basic parallelization concepts and will easily grasp those basics. In two parts, we discuss language features in-depth, with emphasis on advanced features like vectorization and compute acceleration. In the first part, we focus on performance aspects, such as data and thread locality on NUMA architectures, and exploitation of the comparably new language features. The second part is a presentation of the directives for attached compute accelerators. More information

Dmytro Povaliaiev will be part of the Workshop – HPC I/O in the Data Center – Transfer Learning Workflow for I/O Bandwidth Prediction on Thursday, May 25, 2023 9.00 am to 6.00 pm, hall Y2 – 2nd Floor. To effectively manage the data load within a data center, I/O experts must understand how users expect to use these new storage technologies and what services they should provide in order to enhance user productivity. We seek to ensure a systems-level perspective is included in these discussions. The HPC-IODC workshop is a forum to present and discuss work that addresses the storage challenge from a unique perspective, moving the focus from the application-centric perspective to the perspective of data centers and operators. In the workshop, we bring together I/O experts from data centers and application workflows to share current practices for scientific workflows, issues and obstacles for both hardware and the software stack, and R&D to overcome these issues. To focus on relevant aspects and streamline the discussion, a list of relevant topics is provided as the common structure of the talks. The IODC workshop covers three tracks: The research track, the expert talks track, and the student mentoring sessions. Marcel Krüger will present the paper A Case Study on Providing Accessbility-Focused In-Transit Architectures for Neural Network Simulation and Analysis at WOIV on Thursday, May 25 between 9.00 am and 1.00 pm on Hall Y3 – 2nd Floor. Exploring and analyzing the progress and results of scientific simulations needs to be handled efficiently via in-situ/in-transit technologies. Adding these often requires sophisticated prior knowledge or significant changes to the simulation code, resulting in a high entry barrier for users. In this work, the authors report how Insite, a lightweight and accessibility-focused in-transit pipeline, was used in various projects to provide visualization and analysis capability.

Our activities

Advanced OpenMP: Performance and 5.2 Features

Time: Sunday, May 21, 9:00am to 1:00 pm

Presenters: Christian Terboven, NHR4CES, RWTH, Michael Klemm, Bronis R. de Supinski

Venue: Hall Y6, 2nd floor

Current Challenges in Visualization for HPC

How AI, Accessibility and Innovation Change VisualizationRequirements

Time: Monday, May 22, 4:30 pm

Host: Tim Gerrits NHR4CES, RWTH Aachen University

Venue: booth K1004

Guests: James Kress, Francois Mazen, Jens Henrik Göbbert, Michael Böttinger, David Pugmire

NHR: Benchmarks + TCO

Time: Tuesday, May 23, 2:00 pm

Host: Christian Terboven, NHR4CES, RWTH Aachen University

Venue: booth K1004

Guests: Holger Brunst, TU Dresden, tba

Software licenses in NHR

Time: Wednesday, May 24, 12:30 pm to 2:30 pm

Host: Benjamin Juhl, NHR4CES, TU Darmstadt

Venue: booth K1004

Guests: Thomas Zeiser, (Friedrich-Alexander-Universität Erlangen-Nürnberg), Robert Schade (PC2), Marc-Andre Hermanns (RWTH Aachen University)

Teaching Advanced MPI

Time: Wednesday, May 24, 2:00 pm

Host: Marc-Andre Hermanns NHR4CES, RWTH Aachen University

Venue: booth K1004

Guests: Sebastian Potthoff (Westfälische Wilhelms-Universität Münster), Thomas Breuer (Forschungszentrum Jülich), Julian Kunkel (Universität Göttingen)

HPC I/O in the Data Center

Time: Thursday, May 25, 9:00 am to 6:00 pm

Presenters: Dmytro Povaliaiev, Radita Liem, NHR4CES, RWTH

Venue: booth K1004

Guests: tba

Paper Presentation at WOIV: A Case Study on Providing Accessbility-Focused In-Transit Architectures for Neural Network Simulation and Analysis

Time: Thursday, May 25, 9:00 am to 1:00 pm

Presenters: Marcel Krüger, Tim Gerrits, NHR4CES, RWTH

Venue: Hall Y3, 2nd floor